## **Features**

### General

- 0.35µ Process Technology

- Industry-standard M68HC05 Instruction Set, including: 8 x 8 Bits Unsigned Multiply Instruction, True Bit Manipulation, Memory-mapped I/O

- Operating Voltage: 3.0V ± 10% or 5.0V ± 10%

- Meets GSM 11.11 & 11.12 Specifications

- 5.0 MHz Maximum Internal Bus Frequency at 3.0V and 5.0V

- ESD Protection to ± 4000V

- Bond Pad Layout Conforming to ISO Standard ISO 7816/2

- External Maskable Interrupt on ISO Standard I/O Port (PA0)

- Power-saving WAIT and Very Low Power STOP Modes

- Power-up Detection

- Available as Sawn or Unsawn Wafers

#### Contactless Mode

- RF Contactless Interface with Full Support for ISO 14443 Type B Protocol

- Supply Voltage Clamp and Regulation

- Full-bridge Power Rectification

- 3.4 MHz Maximum CPU Clock Frequency

- 13.56 MHz Clock Extraction

- Memory-mapped RF I/O Port

- · Card-to-reader

- Modulation of Incoming RF Carrier by Load Switching

- Generation of 847.5 kHz Subcarrier with BPSK Modulation

- NRZ-L or Manchester Data Encoding

### **EEPROM**

- 8128 bytes of on-chip User EEPROM plus 64 Security Bytes

- 64-byte Write/Program/Erase

- 1 ms Program Time, 1 ms Erase Time

- 10 Years Data Retention

- Typically more than 1,000,000 Write/Erase Cycles

- On-chip Charge Pump for EEPROM Programming Driven by an Internal Oscillator

#### RAM and ROM

- 32752 Bytes of On-chip User ROM plus 16 Bytes Reserved for Vectors

- 1024 Bytes of On-chip RAM with Security Wipe on Selected Areas

## **Peripherals**

- Single Bidirectional I/O Line (1-bit ISO 7816/3 Standard I/O Port)

- Interrupt Driven Serial Communications Interface (SCI) with Transmit/Receive Speeds of up to 1.25 Mbit/s

- Time Base Circuitry (with Preset and Maskable Interrupt Capabilities)

- Watchdog Capability

- Hardware DES Module (Capable of Single Encryption or Decryption in 16 Clock Cycles)

- CRC Module (allowing Generation of Checksums (ISO/IEC 3309))

- Random Number Generator

8-bit

Microcontroller

with

8K EEPROM,

Dual Interface,

and Advanced

Security

Features

AT05SC3208RF

**Preliminary**

**Summary**

# Features (continued)

## Security

- Dedicated Hardware to Resist Power Analysis Attacks

- Featureless ROM

- Low and High Voltage Monitors

- Low and High Temperature Monitors

- Low Frequency Monitor

- High Frequency Filter/Monitor

- Advanced Physical Barrier to Enhance Tamper Resistance

- Illegal Address Reset

- Illegal Opcode Reset

- Memory Partitioning with Address Lockout Reset

- Scrambling Logic

- Tamper Monitor

- Physical Removal of Test Mode when Testing is Complete

## **Development Tools**

- Hardware Emulation Module (for the Motorola MMDS05 Development System)

- Software Simulator based on HIWARE's HI-WAVE Product

# **Description**

The AT05SC3208RF is a new member of Atmel's AT05SC family of single chip microcontrollers. Designed specifically for embedded conditional access systems and other security conscious systems, these devices are based on the industry-standard M68HC05 low-power core and its instruction set, and are manufactured in Atmel's standard 0.35µ process technology.

The AT05SC3208RF is designed to give a high level of protection against physical attack, and includes hardware features to assist in protecting against SPA and DPA attacks. On-board DES, CRC and RNG modules are provided to assist in the design of high-security applications.

On-board memory comprises 32K bytes of ROM, 1K bytes of RAM and 8K bytes of EEPROM. The EEPROM features 64-byte write, 1 ms program time, 1 ms erase time, typi-

cally more than 1,000,000 write/erase cycles, and greater than 10 years data retention.

The AT05SC3208RF has on-board contact and contactless interfaces, and is designed in accordance with the ISO standards for integrated circuit cards (ISO 7816 and ISO 14443), and with GSM specifications 11.11 and 11.12, where appropriate. An on-board serial communications interface is also provided.

Application areas for the AT05SC3208RF include Dual Interface Multifunction Cards, e.g. Transport Card plus Electronic Purse/Bank Card.

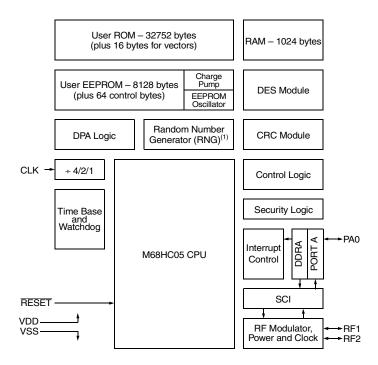

# **Block diagram**

Notes: 1. A sampling/smoothing algorithm MUST be used in conjunction with the RNG to obtain statistically random results across all operating conditions.

#### © Atmel Corporation 2000.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of

Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel Headquarters, 2325 Orchard Parkway, San Jose, CA 95131, TEL (408) 441-0311, FAX (408) 487-2600

Atmel Colorado Springs, 1150 E. Cheyenne Mtn. Blvd., Colorado Springs, CO 80906, TEL (719) 576-3300, FAX (719) 540-1759

Atmel Rousset, Zone Industrielle, 13106 Rousset Cedex, France, TEL (33) 4-4253-6000, FAX (33) 4-4253-6001

Atmel Smart Card ICs, Scottish Enterprise Technology Park, East Kilbride, Scotland G75 0QR, TEL (44) 1355-357000, FAX (44) 1355-242743

Marks bearing  $^{\text{\tiny{8}}}$  and/or  $^{\text{\tiny{TM}}}$  are registered trademarks and trademarks of Atmel Corporation.

Printed on recycled paper. 1508BS-04/00/xM